Procesamiento Personalizado del Arnés de Cableado LVDS

LVDS La señalización diferencial de bajo voltaje es una tecnología de señalización diferencial con bajo consumo de energía, baja tasa de error de bits, baja diafonía y baja radiación. El arnés de cableado LVDS es un canal puente entre la pantalla de visualización y la placa principal de comunicación. Desempeña el papel de fuente de alimentación y transmisión de señal, y la placa principal transmite la imagen a la pantalla de visualización. Esta tecnología de transmisión puede alcanzar más de 155 Mbps. El núcleo de la tecnología VDS es utilizar una oscilación de voltaje muy baja para transmitir datos a alta velocidad, lo que puede realizar una conexión punto a punto o punto a multipunto. El medio de transmisión puede ser una conexión de PCB de cobre o un cable balanceado

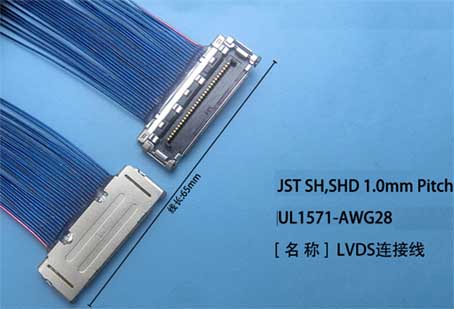

Cables de uso común como: cable UL1571-AWG28 (cuanto mayor es el número, más delgado es el cable).

LVDS es una tecnología de señal diferencial de baja amplitud. Utiliza señales de muy baja amplitud (aproximadamente 350 mV) para transmitir datos a través de un par de trazas de PCB diferenciales o cables balanceados. Puede transmitir datos en serie a velocidades de hasta miles de Mbps. Debido a que la amplitud de la señal de voltaje es baja y se maneja en un modo de fuente de corriente constante, solo produce un ruido extremadamente bajo, consume muy poca energía e incluso el consumo de energía casi no cambia independientemente de la frecuencia. Además, debido a que LVDS transmite datos de manera diferencial, no es susceptible al ruido de modo común.

Con el avance continuo de la tecnología de diseño electrónico, la interconexión de señales de alta velocidad y la aplicación de canales de banda ancha aumentan día a día, y la cantidad de datos que deben transmitirse aumenta y la velocidad es cada vez más rápida. En la actualidad, las interfaces de capa física punto a punto existentes, como RS-422, RS-485, SCSI y otros estándares de transmisión de datos, están inherentemente limitadas en términos de velocidad, ruido, EMI / EMC, consumo de energía y costo. Hágalo cada vez más difícil para aplicaciones prácticas. También con el desarrollo de la tecnología electrónica militar y el campo de las comunicaciones espaciales: Como el sistema de seguimiento y retransmisión de datos por satélite (TDSS), para lograr una retransmisión de datos de alta velocidad y medición de velocidad de rango. Los problemas causados por la alta velocidad de transmisión y la ocupación del ancho de banda deben resolverse primero; En el campo de las aplicaciones de radar, la aparición de varios sistemas nuevos de radar y aplicaciones en diferentes campos, como el reconocimiento de banda ancha y las contramedidas electrónicas, también enfrenta inevitablemente problemas de transmisión y adquisición de datos a alta velocidad; Por lo tanto, el uso de la nueva tecnología de interfaz de E / S para resolver el problema del cuello de botella de la transmisión de datos se ha vuelto cada vez más prominente. Con su bajo voltaje inherente, bajo consumo de energía y características de transmisión de alta velocidad, LVDS se ha convertido cada vez más en el estándar de interfaz preferido para el diseño de sistemas de banda ancha de alta velocidad. En la actualidad, la aplicación de la tecnología LVDS en el campo de las comunicaciones se está volviendo cada vez más popular, especialmente en estaciones base, grandes conmutadores y otros sistemas de transmisión de datos de alta velocidad, LVDS está desempeñando un papel insustituible.

Para adaptarse a la variación de amplio rango del voltaje en modo común, en circunstancias normales, la etapa de entrada del receptor LVDS también incluye un circuito de ajuste de nivel automático, que ajusta el voltaje en modo común a un valor fijo; Detrás hay un flip-flop Schmitt y, para evitar que el flip-flop Scdhmitt sea inestable, el diseño tiene una cierta característica de histéresis y la etapa trasera Schmitt es un amplificador diferencial.

① Capacidad de transmisión de alta velocidad. En el estándar LVDS definido en ANS / EIA / EIA-64, la tasa límite teórica es 1.923Gbps. El modo de trabajo del modo de fuente de corriente constante y la salida de oscilación baja determina la capacidad de conducción a alta velocidad del IVDS.

② Características de bajo consumo de energía. Los dispositivos LVDS se implementan utilizando tecnología CMOS y CMOS puede proporcionar un menor consumo de energía estática; Cuando la corriente de conducción de la fuente de corriente constante es de 3,5 mA, el consumo de energía de la carga (coincidencia de terminales de 100 Ω) es de solo 1,225 mW; El consumo de energía de LVDS es constante, a diferencia del consumo de energía dinámico de los transceptores CMOS que aumentan con respecto a la frecuencia. El diseño del variador del modo de fuente de corriente constante reduce el consumo de energía del sistema y reduce en gran medida la influencia de los componentes de frecuencia en el consumo de energía. Aunque el consumo de energía de CMOS es menor que el de LVDS cuando la velocidad es menor, a medida que aumenta la frecuencia, el consumo de energía de CMOS aumentará gradualmente y, finalmente, necesitará consumir más energía que LVDS. Generalmente, cuando la frecuencia es igual a 200MSps, el consumo de energía de LVDS y CMOS es aproximadamente el mismo.

③ El voltaje de la fuente de alimentación es bajo. Con el desarrollo de circuitos integrados y la necesidad de mayores velocidades de transmisión de datos, la fuente de alimentación de bajo voltaje se ha convertido en una necesidad urgente. Reducir el voltaje de la fuente de alimentación no solo reduce el consumo de energía de los circuitos integrados de alta densidad, sino que también reduce la presión de disipación de calor dentro del chip, lo que ayuda a mejorar la integración. Los controladores y receptores LVDS no dependen de características específicas de voltaje de la fuente de alimentación, lo que determina que ocupe la parte superior en este sentido.

④ Fuerte capacidad anti-ruido. La ventaja inherente de las señales diferenciales es que el ruido se acopla a un par de líneas diferenciales en un modo común y se sustrae en el receptor, de modo que se puede eliminar el ruido. Por lo tanto, LVDS tiene una gran capacidad para resistir el ruido de modo común.

⑤ Suprima eficazmente las interferencias electromagnéticas. Dado que las polaridades de las señales diferenciales son opuestas, los campos electromagnéticos irradiados por ellas pueden anularse entre sí. Cuanto más estrecho es el acoplamiento, menos energía electromagnética se libera al mundo exterior, lo que reduce la EMI.

⑥ Posicionamiento preciso de la sincronización. Porque el cambio de interruptor de la señal diferencial se encuentra en la intersección de las dos señales. A diferencia de las señales ordinarias de un solo extremo, que dependen de voltajes de umbral alto y bajo para juzgar, se ven menos afectadas por el proceso y la temperatura, lo que puede reducir los errores en la sincronización y facilitar la transmisión efectiva de señales digitales de alta velocidad.

⑦ Adáptese al amplio rango de variación de voltaje del plano de tierra. El receptor LVDS puede soportar un cambio de voltaje entre el controlador y el receptor de al menos ± 1V. Dado que el voltaje de polarización típico del controlador IVDS es de + 1,2 V, la suma del cambio de voltaje de tierra, el voltaje de polarización del controlador y el ruido ligeramente acoplado es un voltaje de modo común en la entrada del receptor en relación con la tierra del conductor. Cuando la oscilación no supera los 400 mV, el rango de modo común es de + 0,2 V ~ + 2,2 V y, en general, el rango de voltaje de entrada del receptor puede variar de 0 V a + 2,4 V.

Es precisamente porque LVDS tiene las principales características mencionadas anteriormente: Esto hace que HyperTansport (de AMD), Irfiniband (ly Intel), PCI-Express (de Intel) y otros estándares de bus de E / S de tercera generación (3G IO) usen coincidentemente señalización diferencial de bajo voltaje (IVDS) como la próxima generación de Niveles de señal de alta velocidad estándar.

En el campo de las aplicaciones de radar, con el desarrollo de la tecnología, han aparecido y se han popularizado nuevos radares de sistema, como los radares de sistema DBF, los radares de matriz en fase, etc. El ancho de banda de la señal y el número de canales de señal que deben procesarse han aumentado considerablemente, y se enfrenta el problema de la transmisión de grandes volúmenes de datos. Por lo tanto, se ha convertido en una tendencia inevitable adoptar nuevas tecnologías para resolver el problema de la interfaz de E / S. LVDS, un estándar de interfaz de alta velocidad y baja potencia, permite resolver este problema de cuello de botella en la transmisión. Por lo tanto, la tecnología LVDS se utiliza ampliamente en la actualidad en radares de alta velocidad y sistemas de recepción de alta velocidad; Al utilizar la tecnología LVDS para realizar una interconexión de placa única punto a punto, la estructura del sistema es muy extensible, y se logra una alta integración de tarjetas de línea y varios subsistemas, y puede cumplir completamente con los requisitos de recopilación y transmisión de datos.

En uso civil, esta tecnología puede soportar la transmisión de datos de alta velocidad. Es más adecuado para aplicaciones de estructura de comunicación como estaciones base, conmutadores, multiplexores más / menos, soluciones de aplicación para productos de consumo como decodificadores y enlaces de video domésticos / empresariales, así como equipos médicos de imágenes ultrasónicas y fotocopiadoras digitales. Asegúrese de que la operación de partición del sistema pueda ejercer una mayor flexibilidad. Los ingenieros de diseño de sistemas pueden usar la tecnología LVDS para configurar las secciones de procesamiento de señales analógicas y digitales en diferentes placas de circuito, y luego usar cables o placas posteriores para transmitir la salida de datos digitales por el convertidor A / D para garantizar una mayor flexibilidad en el diseño estructural. En la actualidad, todos los tipos de convertidores AD de alta velocidad básicamente eligen utilizar señales LVDS como formato de salida de los datos muestreados, y la mayoría de sus formas de salida son salidas en paralelo. Al mismo tiempo, los chips dedicados que admiten IWDS y otros intercambios de nivel y los chips dedicados de reducción de velocidad LVDS también están surgiendo en un flujo interminable, representado principalmente por varias empresas extranjeras como MAXM, NI y TI.

Además, LVDS tiene un espacio de aplicación muy amplio en la aplicación de transmisión de datos de alta velocidad, reconocimiento y recepción de radar SAR y transmisión de imágenes digitales de alta velocidad de sistemas de medición y control. Especialmente en los últimos años y en los próximos años, los sectores aeroespacial, militar, de comunicaciones y otros han seguido aumentando su demanda de sistemas de comunicación flexibles de alta velocidad de bits. Por un lado, el núcleo de los sistemas de comunicación tradicionales, filtros, mezcladores y muchos otros enlaces se realiza principalmente mediante dispositivos analógicos, lo que restringe en gran medida la confiabilidad, flexibilidad, actualización y mantenimiento del sistema. Por otro lado, en los últimos 20 años, el rápido desarrollo de la tecnología microelectrónica, los circuitos integrados y la teoría de la comunicación digital ha hecho posible implementar muchos enlaces en un sistema de comunicación de alta tasa de bits utilizando métodos digitales. Según la información obtenida hasta ahora, los países extranjeros han desarrollado con éxito una variedad de procesadores de señales de banda base de alta velocidad de bits, totalmente digitales, flexibles y versátiles de alto rendimiento. En la actualidad, hemos logrado importantes avances en el proceso de investigación de la tecnología de transmisión digital de alta velocidad de bits, y una de las tecnologías clave aplicadas es la tecnología LVDS.

Cables de uso común como: cable UL1571-AWG28 (cuanto mayor es el número, más delgado es el cable).

Resumen de tecnología

LVDS es una tecnología de señal diferencial de baja amplitud. Utiliza señales de muy baja amplitud (aproximadamente 350 mV) para transmitir datos a través de un par de trazas de PCB diferenciales o cables balanceados. Puede transmitir datos en serie a velocidades de hasta miles de Mbps. Debido a que la amplitud de la señal de voltaje es baja y se maneja en un modo de fuente de corriente constante, solo produce un ruido extremadamente bajo, consume muy poca energía e incluso el consumo de energía casi no cambia independientemente de la frecuencia. Además, debido a que LVDS transmite datos de manera diferencial, no es susceptible al ruido de modo común.Con el avance continuo de la tecnología de diseño electrónico, la interconexión de señales de alta velocidad y la aplicación de canales de banda ancha aumentan día a día, y la cantidad de datos que deben transmitirse aumenta y la velocidad es cada vez más rápida. En la actualidad, las interfaces de capa física punto a punto existentes, como RS-422, RS-485, SCSI y otros estándares de transmisión de datos, están inherentemente limitadas en términos de velocidad, ruido, EMI / EMC, consumo de energía y costo. Hágalo cada vez más difícil para aplicaciones prácticas. También con el desarrollo de la tecnología electrónica militar y el campo de las comunicaciones espaciales: Como el sistema de seguimiento y retransmisión de datos por satélite (TDSS), para lograr una retransmisión de datos de alta velocidad y medición de velocidad de rango. Los problemas causados por la alta velocidad de transmisión y la ocupación del ancho de banda deben resolverse primero; En el campo de las aplicaciones de radar, la aparición de varios sistemas nuevos de radar y aplicaciones en diferentes campos, como el reconocimiento de banda ancha y las contramedidas electrónicas, también enfrenta inevitablemente problemas de transmisión y adquisición de datos a alta velocidad; Por lo tanto, el uso de la nueva tecnología de interfaz de E / S para resolver el problema del cuello de botella de la transmisión de datos se ha vuelto cada vez más prominente. Con su bajo voltaje inherente, bajo consumo de energía y características de transmisión de alta velocidad, LVDS se ha convertido cada vez más en el estándar de interfaz preferido para el diseño de sistemas de banda ancha de alta velocidad. En la actualidad, la aplicación de la tecnología LVDS en el campo de las comunicaciones se está volviendo cada vez más popular, especialmente en estaciones base, grandes conmutadores y otros sistemas de transmisión de datos de alta velocidad, LVDS está desempeñando un papel insustituible.

El principio básico del arnés de cableado LVDS

El principio de funcionamiento básico de LVDS se muestra en la Figura 1. El controlador de la fuente consiste en una fuente de corriente constante (generalmente alrededor de 3,5 mA, el máximo no es más de 4 mA) que conduce un par de líneas de señal diferencial. El receptor en el extremo receptor tiene una impedancia de entrada de CC alta, por lo que casi toda la corriente de accionamiento fluye a través de la resistencia de coincidencia del terminal de 100 Ω, y se genera un voltaje de aproximadamente 350 mV en el extremo de entrada del receptor. Cuando el estado de excitación del terminal fuente se invierte y cambia, la dirección de la corriente que fluye a través de la resistencia correspondiente cambia, de modo que se produce un cambio de estado lógico alto y bajo en el terminal receptor.Para adaptarse a la variación de amplio rango del voltaje en modo común, en circunstancias normales, la etapa de entrada del receptor LVDS también incluye un circuito de ajuste de nivel automático, que ajusta el voltaje en modo común a un valor fijo; Detrás hay un flip-flop Schmitt y, para evitar que el flip-flop Scdhmitt sea inestable, el diseño tiene una cierta característica de histéresis y la etapa trasera Schmitt es un amplificador diferencial.

Características técnicas

La razón por la que LVDS se ha convertido en la forma de señal preferida de la interfaz de E / S de alta velocidad actual para resolver las limitaciones de la transmisión de datos de alta velocidad es porque tiene ventajas en la velocidad de transmisión, el consumo de energía, la resistencia al ruido y la EMI.① Capacidad de transmisión de alta velocidad. En el estándar LVDS definido en ANS / EIA / EIA-64, la tasa límite teórica es 1.923Gbps. El modo de trabajo del modo de fuente de corriente constante y la salida de oscilación baja determina la capacidad de conducción a alta velocidad del IVDS.

② Características de bajo consumo de energía. Los dispositivos LVDS se implementan utilizando tecnología CMOS y CMOS puede proporcionar un menor consumo de energía estática; Cuando la corriente de conducción de la fuente de corriente constante es de 3,5 mA, el consumo de energía de la carga (coincidencia de terminales de 100 Ω) es de solo 1,225 mW; El consumo de energía de LVDS es constante, a diferencia del consumo de energía dinámico de los transceptores CMOS que aumentan con respecto a la frecuencia. El diseño del variador del modo de fuente de corriente constante reduce el consumo de energía del sistema y reduce en gran medida la influencia de los componentes de frecuencia en el consumo de energía. Aunque el consumo de energía de CMOS es menor que el de LVDS cuando la velocidad es menor, a medida que aumenta la frecuencia, el consumo de energía de CMOS aumentará gradualmente y, finalmente, necesitará consumir más energía que LVDS. Generalmente, cuando la frecuencia es igual a 200MSps, el consumo de energía de LVDS y CMOS es aproximadamente el mismo.

③ El voltaje de la fuente de alimentación es bajo. Con el desarrollo de circuitos integrados y la necesidad de mayores velocidades de transmisión de datos, la fuente de alimentación de bajo voltaje se ha convertido en una necesidad urgente. Reducir el voltaje de la fuente de alimentación no solo reduce el consumo de energía de los circuitos integrados de alta densidad, sino que también reduce la presión de disipación de calor dentro del chip, lo que ayuda a mejorar la integración. Los controladores y receptores LVDS no dependen de características específicas de voltaje de la fuente de alimentación, lo que determina que ocupe la parte superior en este sentido.

④ Fuerte capacidad anti-ruido. La ventaja inherente de las señales diferenciales es que el ruido se acopla a un par de líneas diferenciales en un modo común y se sustrae en el receptor, de modo que se puede eliminar el ruido. Por lo tanto, LVDS tiene una gran capacidad para resistir el ruido de modo común.

⑤ Suprima eficazmente las interferencias electromagnéticas. Dado que las polaridades de las señales diferenciales son opuestas, los campos electromagnéticos irradiados por ellas pueden anularse entre sí. Cuanto más estrecho es el acoplamiento, menos energía electromagnética se libera al mundo exterior, lo que reduce la EMI.

⑥ Posicionamiento preciso de la sincronización. Porque el cambio de interruptor de la señal diferencial se encuentra en la intersección de las dos señales. A diferencia de las señales ordinarias de un solo extremo, que dependen de voltajes de umbral alto y bajo para juzgar, se ven menos afectadas por el proceso y la temperatura, lo que puede reducir los errores en la sincronización y facilitar la transmisión efectiva de señales digitales de alta velocidad.

⑦ Adáptese al amplio rango de variación de voltaje del plano de tierra. El receptor LVDS puede soportar un cambio de voltaje entre el controlador y el receptor de al menos ± 1V. Dado que el voltaje de polarización típico del controlador IVDS es de + 1,2 V, la suma del cambio de voltaje de tierra, el voltaje de polarización del controlador y el ruido ligeramente acoplado es un voltaje de modo común en la entrada del receptor en relación con la tierra del conductor. Cuando la oscilación no supera los 400 mV, el rango de modo común es de + 0,2 V ~ + 2,2 V y, en general, el rango de voltaje de entrada del receptor puede variar de 0 V a + 2,4 V.

Es precisamente porque LVDS tiene las principales características mencionadas anteriormente: Esto hace que HyperTansport (de AMD), Irfiniband (ly Intel), PCI-Express (de Intel) y otros estándares de bus de E / S de tercera generación (3G IO) usen coincidentemente señalización diferencial de bajo voltaje (IVDS) como la próxima generación de Niveles de señal de alta velocidad estándar.

Aplicación de tecnología

En el campo de las aplicaciones de radar, con el desarrollo de la tecnología, han aparecido y se han popularizado nuevos radares de sistema, como los radares de sistema DBF, los radares de matriz en fase, etc. El ancho de banda de la señal y el número de canales de señal que deben procesarse han aumentado considerablemente, y se enfrenta el problema de la transmisión de grandes volúmenes de datos. Por lo tanto, se ha convertido en una tendencia inevitable adoptar nuevas tecnologías para resolver el problema de la interfaz de E / S. LVDS, un estándar de interfaz de alta velocidad y baja potencia, permite resolver este problema de cuello de botella en la transmisión. Por lo tanto, la tecnología LVDS se utiliza ampliamente en la actualidad en radares de alta velocidad y sistemas de recepción de alta velocidad; Al utilizar la tecnología LVDS para realizar una interconexión de placa única punto a punto, la estructura del sistema es muy extensible, y se logra una alta integración de tarjetas de línea y varios subsistemas, y puede cumplir completamente con los requisitos de recopilación y transmisión de datos.En uso civil, esta tecnología puede soportar la transmisión de datos de alta velocidad. Es más adecuado para aplicaciones de estructura de comunicación como estaciones base, conmutadores, multiplexores más / menos, soluciones de aplicación para productos de consumo como decodificadores y enlaces de video domésticos / empresariales, así como equipos médicos de imágenes ultrasónicas y fotocopiadoras digitales. Asegúrese de que la operación de partición del sistema pueda ejercer una mayor flexibilidad. Los ingenieros de diseño de sistemas pueden usar la tecnología LVDS para configurar las secciones de procesamiento de señales analógicas y digitales en diferentes placas de circuito, y luego usar cables o placas posteriores para transmitir la salida de datos digitales por el convertidor A / D para garantizar una mayor flexibilidad en el diseño estructural. En la actualidad, todos los tipos de convertidores AD de alta velocidad básicamente eligen utilizar señales LVDS como formato de salida de los datos muestreados, y la mayoría de sus formas de salida son salidas en paralelo. Al mismo tiempo, los chips dedicados que admiten IWDS y otros intercambios de nivel y los chips dedicados de reducción de velocidad LVDS también están surgiendo en un flujo interminable, representado principalmente por varias empresas extranjeras como MAXM, NI y TI.

Además, LVDS tiene un espacio de aplicación muy amplio en la aplicación de transmisión de datos de alta velocidad, reconocimiento y recepción de radar SAR y transmisión de imágenes digitales de alta velocidad de sistemas de medición y control. Especialmente en los últimos años y en los próximos años, los sectores aeroespacial, militar, de comunicaciones y otros han seguido aumentando su demanda de sistemas de comunicación flexibles de alta velocidad de bits. Por un lado, el núcleo de los sistemas de comunicación tradicionales, filtros, mezcladores y muchos otros enlaces se realiza principalmente mediante dispositivos analógicos, lo que restringe en gran medida la confiabilidad, flexibilidad, actualización y mantenimiento del sistema. Por otro lado, en los últimos 20 años, el rápido desarrollo de la tecnología microelectrónica, los circuitos integrados y la teoría de la comunicación digital ha hecho posible implementar muchos enlaces en un sistema de comunicación de alta tasa de bits utilizando métodos digitales. Según la información obtenida hasta ahora, los países extranjeros han desarrollado con éxito una variedad de procesadores de señales de banda base de alta velocidad de bits, totalmente digitales, flexibles y versátiles de alto rendimiento. En la actualidad, hemos logrado importantes avances en el proceso de investigación de la tecnología de transmisión digital de alta velocidad de bits, y una de las tecnologías clave aplicadas es la tecnología LVDS.