Technical parameters and working principle of VGA data cable

- PRODUCT DETAIL

What is a VGA data cable?

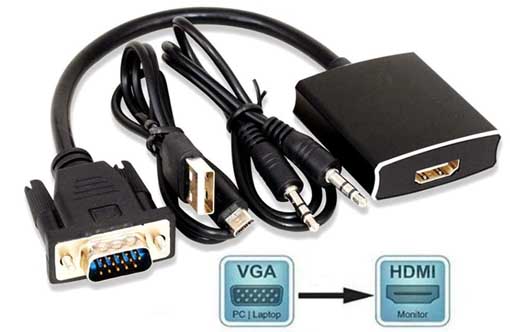

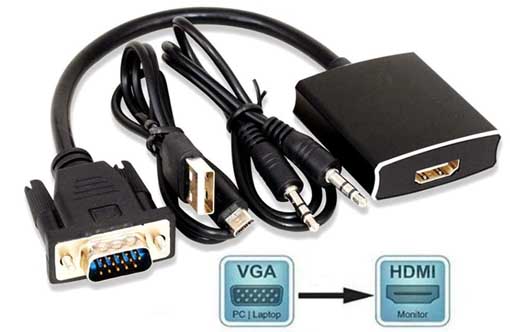

The VGA data cable is a special cable used to connect the VGA interface (D-SUB) of the TV or monitor and the VGA interface (D-SUB) of the graphics card. Most computers and external display devices are connected through an analog VGA interface. The display image information generated in a digital manner inside the computer is converted into R, G, and B primary color signals and line and field synchronization signals by the digital/analog converter in the graphics card. The signal is transmitted to the display device through the data cable. For analog display devices, such as analog CRT displays, the signal is directly sent to the corresponding processing circuit to drive and control the picture tube to generate images. For digital display devices such as LCD and DLP, the display device needs to be equipped with a corresponding A/D (analog/digital) converter to convert analog signals into digital signals. After D/A and A/D2 conversions, some image details will inevitably be lost. It is better to use a DVI or HDMI type data cable to connect to a digital display device.

1.4 Data width and format

If the VGA displays a true color BMP image, it requires 8 bits for each of the three components of R, G, and B, that is, 24 bits represent a pixel value, and in many cases, 32 bits are used to represent a pixel value. In order to save the storage space of the video memory, high-color images can be used, that is, each pixel value is represented by 16 bits, and the three components of R, G, and B use 5 bits, 6 bits, and 5 bits respectively. Compared with the true color image, the data volume is reduced by half, and the display effect can be satisfied at the same time.

(1) Controller: VGA display has multiple modes, which need to be switched between modes through the controller, and the displayed content needs to be received, processed and displayed. Therefore, the higher the performance of the controller, the better the data update and display effect.

(2) Display data buffer area: VGA display requires fast memory speed and large capacity. The reading speed must reach 65MHz or less, and the storage capacity must be at least 2MB. High-speed SRAM or SDRAM can be used as the display data buffer.

(3) Digital to analog converter DAC: VGA display has the following requirements for digital-to-analog conversion DAC: One is high-speed conversion, the conversion speed should be 80MHz or above; Second, it has good rigidity, which can ensure the synchronization of R, G and B signals; The third is the corresponding accuracy. You can choose a dedicated video chip including 3-channel 8-bit high-speed D/A.

(4) Data source and its interface: To improve the efficiency of VGA display, it is necessary to continuously update the data, while ensuring real-time performance, so a very high interface speed is required. Although the VGA display card can reach a data update speed of 100Mbps, general equipment, especially embedded equipment, cannot reach such a high speed, and in most cases such a high data update rate is not required. Commonly used interfaces are EPP interface, USB interface, TCP/IP, RS232C/485, etc. Among them, TCP/IP, EPP interface and USB interface are computer-based, and the speed is faster; TCP/IP and RS232C/485 are interfaces based on network communication. Although RS485 is slow, it is widely used and can realize remote control.

When the data source is a low-speed interface, you can consider using Flash or SM memory card to pre-store some commonly used image display data and font files. These data are directly applied when the data is updated, thereby speeding up the update speed of the display cache. This not only satisfies the display of high-resolution images, but also satisfies the rapid update of text information data. In order to store more images at first, you can store JPEG format images first, and then decode them into BMP bitmap images by the controller and send them to the display buffer for display, thus relatively expanding the storage space of Flash. At the same time, since the decoding speed of the image is much faster than the speed of the data source interface, the data update speed of the display buffer is correspondingly improved.

(1) Using dual-port RAM with cache function, this method uses a large number of devices, high power consumption, and high cost, which is basically undesirable.

(2) Two sets of SRAM are used for ping-pong work mode, one set of SRAM is used for display at the same time, the other set of SRAM is used for image data update, and then the two sets of SRAM are switched. Doing so will increase some costs and require more complex bus control.

(3) Use FPAG/CPLD and SDRAM to construct dual-port SRAM. This method has good real-time performance, low cost, and complicated timing control. It is the best solution to achieve high performance and low cost requirements.

(4) Using a set of SRAM as the video memory can simplify system design and reduce costs. At this time, you can consider using the idle timing segment of the SRAM bus in the line timing and frame timing to realize the data update of the display memory SRAM without turning off the image display. The update rate of this method is closely related to the data writing speed. The faster the video memory write data, the higher the update rate of this method.

It is assumed that the maximum working clock of the CPU is 60MHz, and the JPEG decoding update method is adopted. At this time, if the decoding buffer area is allocated to the on-chip memory of the CPU, when updating the data, the data is written directly from the memory to the SRAM, which takes 0.17μs at a time; If the decoding buffer area is allocated in the off-chip space, the CPU must first read the data off-chip and then write the data to the SRAM when updating the data, so that a write takes 0.25μs. When there is only a partial difference between two adjacently displayed images or the text display information is updated, a partial data update method can be used to increase the update rate. Table 2 shows the bus idle time contained in each frame of image, and the frame rate for all image updates and 10% partial updates under different decoding buffer allocation methods. The frame rate mentioned here refers to the update speed of the video memory data, not the screen refresh rate of the image, it has no effect on the refresh rate.

The embedded VGA display system designed based on the above scheme realizes the embedded high-resolution VGA display with only the system control board and CRT display.

Through the design analysis and actual use of the embedded VGA display system, the following conclusions are obtained:

(1) Since VGA display is a high-speed process, high-speed devices should be selected when selecting devices.

(2) VGA display timing requirements are stricter, the front and rear edges and sync pulse width in the timing must be set according to strict reference data.

(3) In general, due to the limitation of the data interface, the data update rate cannot reach the level of the computer. Through some special designs, it can still meet the needs of most embedded VGAs.

(4) Performance, cost and complexity should be considered comprehensively, and the actual needs of the system should be taken as the goal, and reasonable and practical design schemes should be adopted.

This standard is already very outdated for today's personal computer market. Even so, VGA is still a low standard supported by most manufacturers, and personal computers must support the VGA standard before loading their own unique drivers.

In summary, CGA and EGA can only display 16 colors at the same time, while VGA uses Mode 13h. It can display all the colors in the 256-color plate at one time, and the 256 colors are selected from 262,144 colors.

The VGA data cable is a special cable used to connect the VGA interface (D-SUB) of the TV or monitor and the VGA interface (D-SUB) of the graphics card. Most computers and external display devices are connected through an analog VGA interface. The display image information generated in a digital manner inside the computer is converted into R, G, and B primary color signals and line and field synchronization signals by the digital/analog converter in the graphics card. The signal is transmitted to the display device through the data cable. For analog display devices, such as analog CRT displays, the signal is directly sent to the corresponding processing circuit to drive and control the picture tube to generate images. For digital display devices such as LCD and DLP, the display device needs to be equipped with a corresponding A/D (analog/digital) converter to convert analog signals into digital signals. After D/A and A/D2 conversions, some image details will inevitably be lost. It is better to use a DVI or HDMI type data cable to connect to a digital display device.

The working principle of VGA data cable

VGA (Video Graphics Array) is a video transmission standard introduced by IBM in 1987 with the PS/2 machine. It has the advantages of high resolution, fast display rate, and rich colors, and has been widely used in the field of color displays.

The application of VGA technology is also mainly based on VGA display card computers, notebooks and other equipment. However, in some devices that require the display of color high-resolution images and no need to use a computer, the application of VGA technology is rarely seen.

The embedded VGA display system based on this design method can display and control VGA images without using a VGA display card and a computer. The system can be widely used in the display of advertising and prompt information in supermarkets, stations, airports and other public places, and can also be used in the display of operating information in the production process of the factory workshop. It can also be used in daily life in the form of multimedia.

1. Display principle and VGA timing realization

The general VGA display card system is mainly composed of three parts: control circuit, display buffer area and video BIOS program. The control circuit is shown in Figure 1. The control circuit mainly completes the functions of timing generation, display buffer data operation, master clock selection and D/A conversion; The display buffer provides display data buffer space; The video BIOS is solidified in the ROM of the display card as a control program.

1.1 VGA timing analysis

Through the analysis of the basic working principle of the VGA display card, it can be known that to realize the VGA display, it is necessary to solve the problems of data source, data storage, and timing realization. The key is how to implement VGA timing. The standard reference display sequence of VGA is shown in Figure 2. Both line timing and frame timing need to generate four parts: sync pulse (Sync a), display back edge (Back porch b), display time segment (Display interval c) and display front edge (Front porch d). The timing parameters of several commonly used modes are shown in Table 1.

1.2 VGA timing realization

First, determine the main clock frequency according to the refresh frequency, and then calculate the total number of line cycles from the main clock frequency and image resolution. Then the time of each time sequence of a, b, c, d given in Table 1 is converted into the number of clock cycles according to the frequency of the main counting pulse source. In the CPLD, counters and RS flip-flops are used to generate pulse signals of different widths and cycles based on the calculated clock cycles of each timing segment. Reuse their logical combination to form each time sequence of a, b, c, d in Figure 2 and the blank signal BLANK and synchronization signal SYNC of the D/A converter.

1.3 How to read SRAM address

The main clock is used as the pixel count pulse signal, and it also provides the read signal of the display memory SRAM and the D/A conversion clock. The output of the counter driven by it is used as the low address of reading SRAM. The line synchronization signal is used as the line count pulse signal, and the output of the counter driven by it is used as the high address of reading SRAM. Since two pieces of SRAM are used, the highest address is used as the chip select of SRAM. Because there is a certain time delay when the signal passes through the internal logic device of the CPLD, when the CPLD generates the address and read signal to read data, the read signal, address signal and data signal cannot meet the timing requirements of the SRAM to read data. The hardware circuit can be used to make certain timing adjustments for the read signals, so that the timing requirements for reading SRAM and inputting data for the DAC can be met between the signals.

1.4 Data width and format

If the VGA displays a true color BMP image, it requires 8 bits for each of the three components of R, G, and B, that is, 24 bits represent a pixel value, and in many cases, 32 bits are used to represent a pixel value. In order to save the storage space of the video memory, high-color images can be used, that is, each pixel value is represented by 16 bits, and the three components of R, G, and B use 5 bits, 6 bits, and 5 bits respectively. Compared with the true color image, the data volume is reduced by half, and the display effect can be satisfied at the same time.

The application of VGA technology is also mainly based on VGA display card computers, notebooks and other equipment. However, in some devices that require the display of color high-resolution images and no need to use a computer, the application of VGA technology is rarely seen.

The embedded VGA display system based on this design method can display and control VGA images without using a VGA display card and a computer. The system can be widely used in the display of advertising and prompt information in supermarkets, stations, airports and other public places, and can also be used in the display of operating information in the production process of the factory workshop. It can also be used in daily life in the form of multimedia.

1. Display principle and VGA timing realization

The general VGA display card system is mainly composed of three parts: control circuit, display buffer area and video BIOS program. The control circuit is shown in Figure 1. The control circuit mainly completes the functions of timing generation, display buffer data operation, master clock selection and D/A conversion; The display buffer provides display data buffer space; The video BIOS is solidified in the ROM of the display card as a control program.

1.1 VGA timing analysis

Through the analysis of the basic working principle of the VGA display card, it can be known that to realize the VGA display, it is necessary to solve the problems of data source, data storage, and timing realization. The key is how to implement VGA timing. The standard reference display sequence of VGA is shown in Figure 2. Both line timing and frame timing need to generate four parts: sync pulse (Sync a), display back edge (Back porch b), display time segment (Display interval c) and display front edge (Front porch d). The timing parameters of several commonly used modes are shown in Table 1.

1.2 VGA timing realization

First, determine the main clock frequency according to the refresh frequency, and then calculate the total number of line cycles from the main clock frequency and image resolution. Then the time of each time sequence of a, b, c, d given in Table 1 is converted into the number of clock cycles according to the frequency of the main counting pulse source. In the CPLD, counters and RS flip-flops are used to generate pulse signals of different widths and cycles based on the calculated clock cycles of each timing segment. Reuse their logical combination to form each time sequence of a, b, c, d in Figure 2 and the blank signal BLANK and synchronization signal SYNC of the D/A converter.

1.3 How to read SRAM address

The main clock is used as the pixel count pulse signal, and it also provides the read signal of the display memory SRAM and the D/A conversion clock. The output of the counter driven by it is used as the low address of reading SRAM. The line synchronization signal is used as the line count pulse signal, and the output of the counter driven by it is used as the high address of reading SRAM. Since two pieces of SRAM are used, the highest address is used as the chip select of SRAM. Because there is a certain time delay when the signal passes through the internal logic device of the CPLD, when the CPLD generates the address and read signal to read data, the read signal, address signal and data signal cannot meet the timing requirements of the SRAM to read data. The hardware circuit can be used to make certain timing adjustments for the read signals, so that the timing requirements for reading SRAM and inputting data for the DAC can be met between the signals.

1.4 Data width and format

If the VGA displays a true color BMP image, it requires 8 bits for each of the three components of R, G, and B, that is, 24 bits represent a pixel value, and in many cases, 32 bits are used to represent a pixel value. In order to save the storage space of the video memory, high-color images can be used, that is, each pixel value is represented by 16 bits, and the three components of R, G, and B use 5 bits, 6 bits, and 5 bits respectively. Compared with the true color image, the data volume is reduced by half, and the display effect can be satisfied at the same time.

2. Functional unit design

To realize VGA display, in addition to realizing timing control, other functional units must be supported to realize complete image display.

(1) Controller:

VGA display has multiple modes, which need to be switched between modes through the controller, and the displayed content needs to be received, processed and displayed. Therefore, the higher the performance of the controller, the better the data update and display effect.

(2) Display data buffer area:

VGA display requires fast memory speed and large capacity. The reading speed must reach 65MHz or less, and the storage capacity must be at least 2MB. High-speed SRAM or SDRAM can be used as the display data buffer.

(1) Controller:

VGA display has multiple modes, which need to be switched between modes through the controller, and the displayed content needs to be received, processed and displayed. Therefore, the higher the performance of the controller, the better the data update and display effect.

(2) Display data buffer area:

VGA display requires fast memory speed and large capacity. The reading speed must reach 65MHz or less, and the storage capacity must be at least 2MB. High-speed SRAM or SDRAM can be used as the display data buffer.

1.4 Data width and format

If the VGA displays a true color BMP image, it requires 8 bits for each of the three components of R, G, and B, that is, 24 bits represent a pixel value, and in many cases, 32 bits are used to represent a pixel value. In order to save the storage space of the video memory, high-color images can be used, that is, each pixel value is represented by 16 bits, and the three components of R, G, and B use 5 bits, 6 bits, and 5 bits respectively. Compared with the true color image, the data volume is reduced by half, and the display effect can be satisfied at the same time.

2. Functional unit design

To realize VGA display, in addition to realizing timing control, other functional units must be supported to realize complete image display.(1) Controller: VGA display has multiple modes, which need to be switched between modes through the controller, and the displayed content needs to be received, processed and displayed. Therefore, the higher the performance of the controller, the better the data update and display effect.

(2) Display data buffer area: VGA display requires fast memory speed and large capacity. The reading speed must reach 65MHz or less, and the storage capacity must be at least 2MB. High-speed SRAM or SDRAM can be used as the display data buffer.

(3) Digital to analog converter DAC: VGA display has the following requirements for digital-to-analog conversion DAC: One is high-speed conversion, the conversion speed should be 80MHz or above; Second, it has good rigidity, which can ensure the synchronization of R, G and B signals; The third is the corresponding accuracy. You can choose a dedicated video chip including 3-channel 8-bit high-speed D/A.

(4) Data source and its interface: To improve the efficiency of VGA display, it is necessary to continuously update the data, while ensuring real-time performance, so a very high interface speed is required. Although the VGA display card can reach a data update speed of 100Mbps, general equipment, especially embedded equipment, cannot reach such a high speed, and in most cases such a high data update rate is not required. Commonly used interfaces are EPP interface, USB interface, TCP/IP, RS232C/485, etc. Among them, TCP/IP, EPP interface and USB interface are computer-based, and the speed is faster; TCP/IP and RS232C/485 are interfaces based on network communication. Although RS485 is slow, it is widely used and can realize remote control.

When the data source is a low-speed interface, you can consider using Flash or SM memory card to pre-store some commonly used image display data and font files. These data are directly applied when the data is updated, thereby speeding up the update speed of the display cache. This not only satisfies the display of high-resolution images, but also satisfies the rapid update of text information data. In order to store more images at first, you can store JPEG format images first, and then decode them into BMP bitmap images by the controller and send them to the display buffer for display, thus relatively expanding the storage space of Flash. At the same time, since the decoding speed of the image is much faster than the speed of the data source interface, the data update speed of the display buffer is correspondingly improved.

3 Synchronous realization of video memory data update and display

When VGA is displayed, it is necessary to consider how to realize the synchronization of video memory data update and display. There are several solutions:(1) Using dual-port RAM with cache function, this method uses a large number of devices, high power consumption, and high cost, which is basically undesirable.

(2) Two sets of SRAM are used for ping-pong work mode, one set of SRAM is used for display at the same time, the other set of SRAM is used for image data update, and then the two sets of SRAM are switched. Doing so will increase some costs and require more complex bus control.

(3) Use FPAG/CPLD and SDRAM to construct dual-port SRAM. This method has good real-time performance, low cost, and complicated timing control. It is the best solution to achieve high performance and low cost requirements.

(4) Using a set of SRAM as the video memory can simplify system design and reduce costs. At this time, you can consider using the idle timing segment of the SRAM bus in the line timing and frame timing to realize the data update of the display memory SRAM without turning off the image display. The update rate of this method is closely related to the data writing speed. The faster the video memory write data, the higher the update rate of this method.

It is assumed that the maximum working clock of the CPU is 60MHz, and the JPEG decoding update method is adopted. At this time, if the decoding buffer area is allocated to the on-chip memory of the CPU, when updating the data, the data is written directly from the memory to the SRAM, which takes 0.17μs at a time; If the decoding buffer area is allocated in the off-chip space, the CPU must first read the data off-chip and then write the data to the SRAM when updating the data, so that a write takes 0.25μs. When there is only a partial difference between two adjacently displayed images or the text display information is updated, a partial data update method can be used to increase the update rate. Table 2 shows the bus idle time contained in each frame of image, and the frame rate for all image updates and 10% partial updates under different decoding buffer allocation methods. The frame rate mentioned here refers to the update speed of the video memory data, not the screen refresh rate of the image, it has no effect on the refresh rate.

The embedded VGA display system designed based on the above scheme realizes the embedded high-resolution VGA display with only the system control board and CRT display.

Through the design analysis and actual use of the embedded VGA display system, the following conclusions are obtained:

(1) Since VGA display is a high-speed process, high-speed devices should be selected when selecting devices.

(2) VGA display timing requirements are stricter, the front and rear edges and sync pulse width in the timing must be set according to strict reference data.

(3) In general, due to the limitation of the data interface, the data update rate cannot reach the level of the computer. Through some special designs, it can still meet the needs of most embedded VGAs.

(4) Performance, cost and complexity should be considered comprehensively, and the actual needs of the system should be taken as the goal, and reasonable and practical design schemes should be adopted.

This standard is already very outdated for today's personal computer market. Even so, VGA is still a low standard supported by most manufacturers, and personal computers must support the VGA standard before loading their own unique drivers.

The term VGA is often used directly to refer to the resolution of 640×480 regardless of the graphics device. The VGA device can store 4 complete EGA color plates at the same time, and they can quickly switch between them, which looks like instant color changes on the screen.

In addition to the EGA-style color version expanded to 256 colors, these 256 colors can actually be specified as any color through VGA DAC (Digital-to-analog converter). This changes the original EGA color plate rules to a certain extent, because originally on EGA, this is just a way for the program to select the most multiple colors for each channel (ie, red, green and blue) under 2 bits. But under VGA, it is just a simple table of 64 colors, each of which can be changed individually. For example, the first two bits of EGA color represent the amount of red, which is not necessarily the case in VGA.

In addition to the EGA-style color version expanded to 256 colors, these 256 colors can actually be specified as any color through VGA DAC (Digital-to-analog converter). This changes the original EGA color plate rules to a certain extent, because originally on EGA, this is just a way for the program to select the most multiple colors for each channel (ie, red, green and blue) under 2 bits. But under VGA, it is just a simple table of 64 colors, each of which can be changed individually. For example, the first two bits of EGA color represent the amount of red, which is not necessarily the case in VGA.

When VGA specifies the color of the color plate, a color channel has 6 bits, each of which has 64 different changes for red, green, and blue, so there are a total of 262,144 colors. Any of the 256 colors can be selected as the color plate color (and any 16 of the 256 can be used to display the colors of the CGA mode).

This method finally still enables the VGA mode to use unprecedented colors when displaying EGA and CGA modes, because VGA uses an analog way to draw EGA and CGA pictures. Provide an example of color plate conversion: To set the character color of the text mode to dark red, dark red must be a color in the CGA 16 color set (for example, instead of CGA's default No. 7 gray). This No. 7 position will be designated as No. 42 in the EGA color plate, and then the VGA DAC will designate EGA #42 as dark red. The original CGA No. 7 gray on the screen will all become dark red. This technique is often used in 256-color VGA DOS games to indicate the fade-in and fade-out screen of loading games.

This method finally still enables the VGA mode to use unprecedented colors when displaying EGA and CGA modes, because VGA uses an analog way to draw EGA and CGA pictures. Provide an example of color plate conversion: To set the character color of the text mode to dark red, dark red must be a color in the CGA 16 color set (for example, instead of CGA's default No. 7 gray). This No. 7 position will be designated as No. 42 in the EGA color plate, and then the VGA DAC will designate EGA #42 as dark red. The original CGA No. 7 gray on the screen will all become dark red. This technique is often used in 256-color VGA DOS games to indicate the fade-in and fade-out screen of loading games.

In summary, CGA and EGA can only display 16 colors at the same time, while VGA uses Mode 13h. It can display all the colors in the 256-color plate at one time, and the 256 colors are selected from 262,144 colors.